...

The Verifiable Delay Function (VDF) used in the ASIC is based on the work of Benjamin Wesolowski: Efficient verifiable delay functions

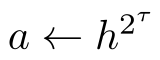

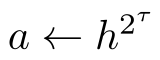

The VDF result is generated by the following formula with the input hash and difficulty :

Typically will be on the order of 240.

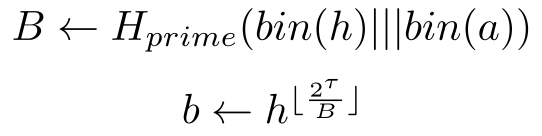

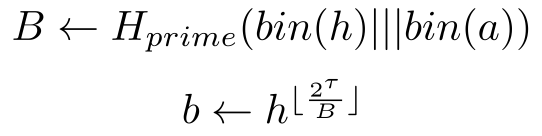

The proof is calculated by:

For more information on VDF’s refer to the project research page: VDF Research

...

There are five main blocks in the VDF ASIC: Modular Squaring Unit, Input/Output Logic, Control Logic, PLL, and Thermal Sensor.

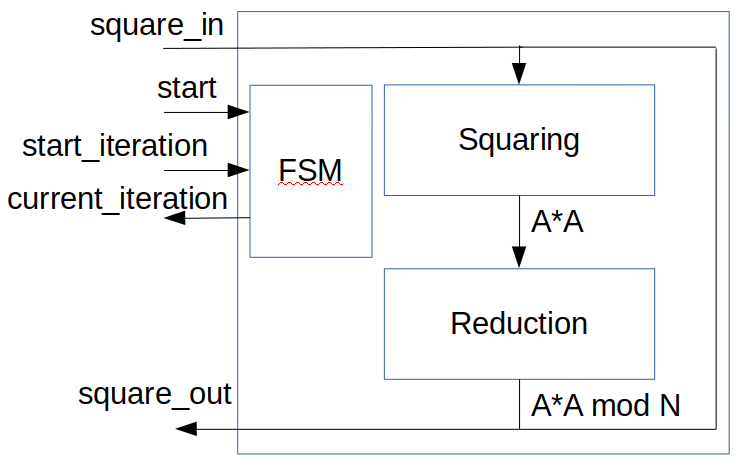

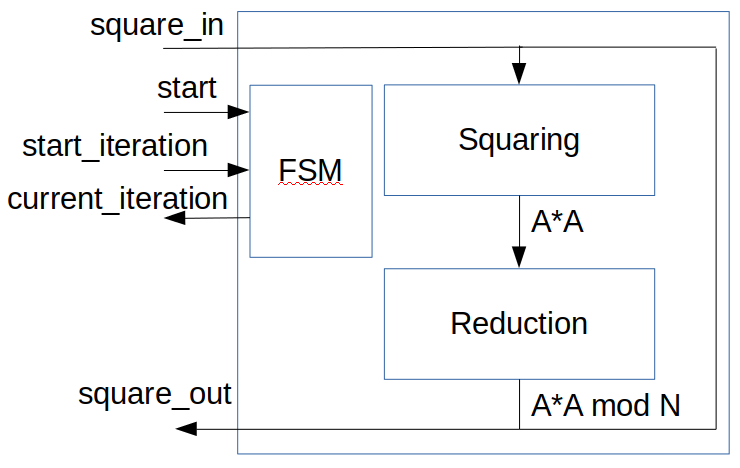

Modular Squaring Unit

The Modular Squaring Unit (MSU) is the primary compute engine in the VDF ASIC. The engine takes a 2048 bit input and returns where is a predefined 2048 RSA modulus. There is a built-in feedback loop that continuously takes the output of the current result as the input to next. This is required for the iterative modular squaring of the VDF evaluation function.

The MSU has control logic around the compute engine to keep track of the current iteration and optionally return intermediate values for use in proof generation. Note the proof generation aspect of VDFs is not applicable in this ASIC.

Input/Output Interface

...

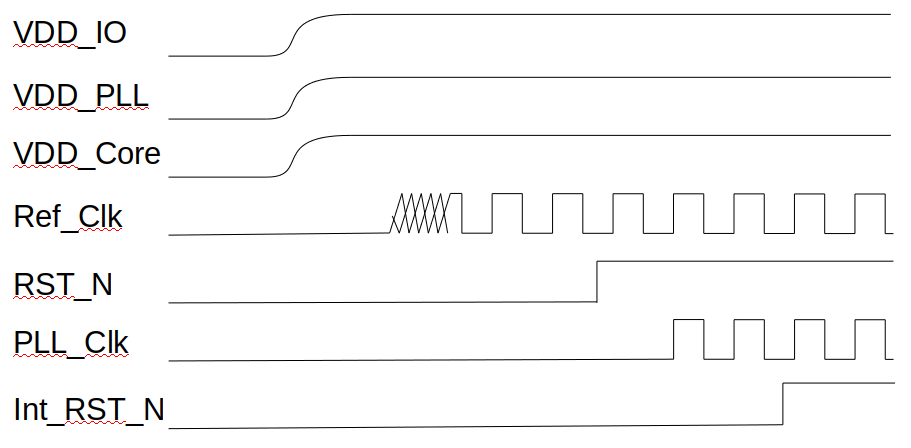

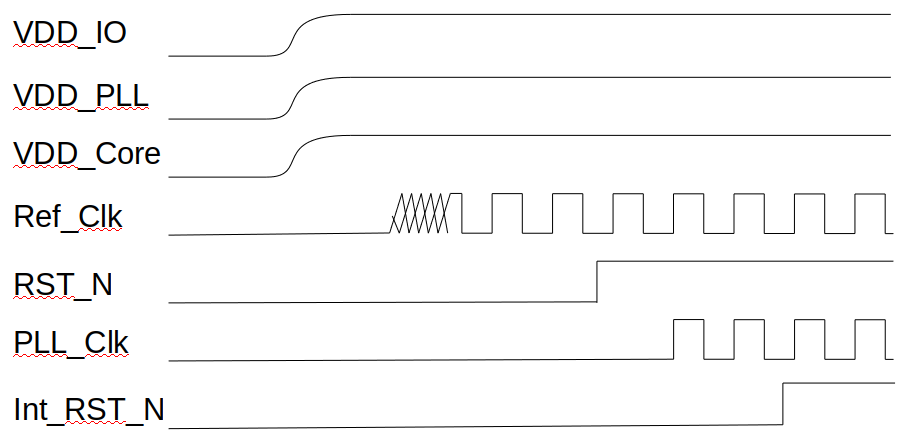

The PLL reference clock should be operation for some period of time prior to flipping the reset pin.

Debug

Options

Clock mux, ability to use ref clk as internal clock

...